# **DSP Filter System**

| Author:   | Nels Pearson |

|-----------|--------------|

| Org Date: | July 5, 2007 |

| Rev Date: | July 6, 2007 |

Doc Number: AIGO-009

| Table of Contents                           |     |

|---------------------------------------------|-----|

| Introduction                                | . 3 |

| Overview                                    |     |

| A2D Input Filter Board                      | .4  |

| Overview                                    | .4  |

| Input Isolation                             | .4  |

| Four Pole Butterworth Anti-aliasing Filter  | .4  |

| Fully Differential Output Section           | . 5 |

| Digital Line                                | . 5 |

| Local Voltage Regulators                    | . 5 |

| Grounds                                     | . 5 |

| Test Points                                 | . 5 |

| Circuit Description                         | . 5 |

| Input Isolation                             |     |

| Four Pole Butterworth Anti-aliasing Filter  | .6  |

| Fully Differential Output Section           |     |

| Digital Line                                | .6  |

| Local Voltage Regulators                    | .7  |

| Grounds                                     | .7  |

| Test Points                                 | .7  |

| Physical                                    | .7  |

| D2A Output Filter Board                     | .8  |

| Overview                                    |     |

| Buffer                                      |     |

| Four Pole Butterworth Reconstruction Filter | . 8 |

| Output Isolation                            |     |

| Digital Line                                |     |

| Local Voltage Regulators                    |     |

| Grounds                                     |     |

| Test Points                                 |     |

| Circuit Description                         |     |

| Buffer                                      |     |

| Four Pole Butterworth Reconstruction Filter |     |

| Output Isolation                            |     |

| Digital Line                                |     |

| Local Voltage Regulators                    |     |

| Grounds                                     | 11  |

| Test Points                                 |     |

| Physical                                    |     |

| 1                                           | 12  |

|                                             | 12  |

| 5                                           | 12  |

| 0                                           | 12  |

|                                             | 12  |

| Physical                                    | 13  |

## Table of Co

## Introduction

This document describes the signal conditioning hardware design for the DSP Filter System. Various sections describe the input cards, output cards, and the backplane.

The main purpose of the system is to support AIGO test mass control. The general specifications for the overall system are:

Channel Bandwidth = 200 Hz Sample Rate = 10 kHz Data Resolution = 16 bit (> 90 db [nom 84 db]) Low pass Filter (anti-aliasing / reconstruction) = 2 kHz Surface mount components 3U EURO Card form factor and 19" rack mount

The system was generated using the DXP 2004 schematic capture and PCB development software during June and July of 2007.

## Overview

The hardware consists of a 3U backplane for a 19" rack, 4 input anti-aliasing filter cards, and 4 output reconstruction filter cards. The input and output cards are based on the 3U EURO card form factor and interface to the DIN 41612 IEC 60603-2 connectors on the backplane. The system conforms to IEC 297-3 to the extent possible.

## A2D Input Filter Board

The Input Filter Board is a four channel signal conditioning 3U Euro card used to provide input isolation, anti-aliasing filters, and differential drive to a SI\_C33DSP/MOD\_6800 data acquisition and processing PC/PCI board controlled through National Instruments LabView software. Signal connections are through standard BNC connectors provided on the front of the card. There will be four of these cards, along with similar output cards, mounted in a 3U 19" rack in a typical system.

#### **Overview**

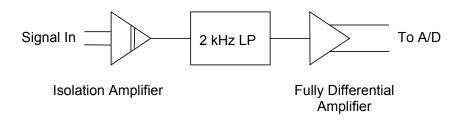

The board provides four channels of input signal conditioning for the data acquisition system with output signals up to  $\pm$  10 volts. Each input channel consists of an isolation amplifier (AD203SN), a four pole Butterworth filter (OP27GS), and a fully differential output amplifier (THS4150). Most of the components are surface mount. There are also local voltage regulators to provide the  $\pm$ 15v & -15v for the active components.

The channels are initially set for an overall gain of 2 with low DC offset and a 2 kHz low pass bandwidth. The gain limits input signals to +/- 5 volts.

#### Input Isolation

The AD203SN 10 kHz Bandwidth Isolation Amplifier provides total galvanic isolation between the input and output sections, including the power supplies. It is initially configured for an input gain of 2 and a table provides resistor values for other gains of 1 and 5. The AD203SN has an internal 10 kHz low pass filter in its output section. See the data sheet for additional specifications on this device.

The AD203SN also provides isolated +15vdc @ 5 ma to power additional input conditioning circuitry as needed. This power is available from a 2-pin header located near the associated channel's BNC connector at the front of the board.

#### Four Pole Butterworth Anti-aliasing Filter

The anti-aliasing filter is constructed from two 2-pole unity gain Sallen-Key low pass filter sections using OP27GS devices. The -3 db point is set at 2 kHz. The frequency setting capacitors use the larger 1206 form factor to provide for a wider selection of capacitor values in future revisions of the circuit.

## **Fully Differential Output Section**

The THS4150 provides differential drive to the DSP A/D converter for noise reduction. The unity gain and 390 ohm resistor values are recommended by manufacture for optimal CMRR and minimal DC offset. The larger 0805 1/4w package is used for the resistors due to the 10 volt signal levels that may be encountered.

#### **Digital Line**

The SAMPLE\_CLK\_IO and DGND lines are routed to the board for future expansion. This line can be configures as an external clock or as a general purpose IO line. Since it is routed to each of the cards, signals on this line will be common to all cards.

#### Local Voltage Regulators

The LM340 and LM7915 devices provide up to 1A of +15v and -15v, respectively from the backplane +/- 18 VDC supplies. The LM340 provides 70 db of ripple rejection with a nominal 90  $\mu$ V of output noise voltage. Similarly, the LM7915 provides 70 db of ripple rejection with a nominal 375  $\mu$ V of output noise voltage.

#### Grounds

All of the circuits, except for the isolated input section, use power GND as a reference. The AGND from the DSP A/D module is tied to GND at one point on the card with a single trace.

#### **Test Points**

Test points are provided at the input, after each circuit section, and the output to allow for complete analysis of the channel. Only the test points around the filter are ground referenced. The initial input and final output test points are differential.

## **Circuit Description**

A component level description of each circuit area is presented to provide insight into the design decisions and concepts used during the development of the Input Filter Board to add in future analysis.

The board contains four identical signal channels. Channel 1 (CH1) will be used as the reference design for all further discussions.

#### Input Isolation

The AD203SN device (U3) decouples the system from the input transducer to reduce ground referencing problems. It is the military version of the AD202/AD204 series and has some minor improvements in its specifications. It is also used in other designs of LIGO type instrumentation. Although not pin-for-pin equivalent, the AD202k and AD204k devices should be considered as replacements and evaluated for future designs.

The gain of U3 is set by R1 and R2 as it is configured as a standard noninverting op amp. A table is provided for other typical gains. Since the input signals are expected to reach values between 1 and 2 volts, care should be used when configuring the device for gains above 5.

There is a decoupling capacitor, C5, that has been provide per general design principles, but may be removed in future designs.

There is an integrated 12 kHz low pass filter in the output section that established the full power bandwidth at 10 kHz.

U3 provides an isolated power supply output of +15vdc @ 5ma maximum to power external signal conditioning components. The device does not provide short circuit protection on this output, so care should be taken when using it.

#### Four Pole Butterworth Anti-aliasing Filter

The anti-aliasing filter is standard design based on two 2-pole unity gain Sallen-Key low pass filters with their parameters adjusted for a cascaded operation to achieve a frequency ( $f_c$ ) response of 2 kHz. The general formulas are

$$R_{1,2} = \frac{a_i C_1 \mp \sqrt{a_i^2 C_2^2 - 4b_i C_1 C_2}}{4\pi f_c C_1 C_2}$$

(1)

$$C_2 \ge C_1 \frac{4b_i}{a_i^2}$$

(2)

and use the coefficients for a Butterworth filter (n=4) from Table 1.

| section | ai     | b <sub>i</sub> | Q    |

|---------|--------|----------------|------|

| 1       | 1.8478 | 1.0000         | 0.54 |

| 2       | 0.7654 | 1.0000         | 1.31 |

#### **Table 1 Low Pass Butterworth Filter Coefficients**

The Butterworth filter style was selected to provide maximum flat in-band response.

The frequency setting capacitors C12, C13, C14, and C15 use the 1206 surface mount package to provide value selections up to 4700 pf for COG high stability capacitors.

Power supply decoupling is provided through C6, C7, C8 and C9 that are placed close to their respective device power pins.

R5 & R6 and R9 & R10 are provided for the general Sallen-Key configuration to allow for future design changes.

The OP27 devices are used due to their low noise characteristics. The AD27GS is the only one of the family available in a surface mount package (SO-8). The AD27EP or AD27EZ (DIP-8) should be considered in future designs due to its improved specifications.

## **Fully Differential Output Section**

The THS4150 device (U6) provides differential drive to the DSP A/D converter for noise reduction. The device is configured for unity gain by R11, R12 R13, and R14. The value of 390 ohms is recommended by the manufacture for G = 1. Since there is a virtual ground at the input pins of the op amp, the current for input signals of 10v can exceed 25 ma leading to a power dissipation of 250 mw. Therefore, the larger 1206 size is used for these devices.

#### **Digital Line**

The SAMPLE\_CLK\_IO and DGND lines are available on the board for future use. A typical use might be to deliver an over voltage detection signal, derived from

added circuitry, back to the DSP controller. This line would then be wire-or'd between all of the input boards.

## **Local Voltage Regulators**

The LM340 (U1) and LM7915 (U2) devices provide on board voltage regulation of up to 1A of +15v and -15v respectively. They exhibit the best overall power supply noise of three terminal devices. They are mounted vertically to allow heat sinks to be attached if needed at a later date.

They each have the recommended decoupling capacitors of 0.22uF (input) and 0.1uF (output) per the manufacture's data sheets.

### Grounds

All of the circuits, except for the isolated input section, use power GND as a reference. The AGND from the DSP A/D module is tied to power supply GND at one point on the card near the P1 connector with a single 20mil trace.

### **Test Points**

Test point TP1 provides both of input lines from the BNC connector and is not referenced to GND. Test points TP2 (input), TP3 (midsection), and TP4 (output) are used to characterise the low pass filter and are referenced to GND. The differential outputs of U6 are tied to TP5, which is not referenced to GND.

## Physical

The Input Filter Board conforms to IEC 297-3 for 3U EURO cards with a DIN 41612 Type C 96 pin IEC 60603-2 style connector.

The board measures 6.299 mil x 3.937 mil and is a 62 mil two layer board. The majority of the solder side is composed of a ground plane.

## **D2A Output Filter Board**

The Output Filter Board is a four channel signal conditioning 3U Euro card used to provide reconstruction filters and output isolation for a SI\_C33DSP/MOD\_6800 data acquisition and processing PC/PCI board controlled through National Instruments LabView software. Signal connections are through standard BNC connectors provided on the front of the card. There will be four of these cards, along with similar input cards, mounted in a 3U 19" rack in a typical system.

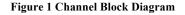

#### **Overview**

The board provides four channels of output signal conditioning for the control system with output signals of up to +/- 10 volts. Each output channel consists of a buffer (OP27GS), a four pole Butterworth filter (OP27GS), and an output isolation amplifier (AD210SN). Most of the components are surface mount. There are also local voltage regulators to provide the +15v & -15v for the active components.

The channels are set for an overall gain of 1 with low DC offset and a 2 kHz low pass bandwidth.

Figure 2 Output Channel Block Diagram

## **Buffer**

There is a unity gain buffer for the single ended DAC signal from the DSP module. There is also an optional 47k ohm resistor to give a nominal load to the DAC output.

## Four Pole Butterworth Reconstruction Filter

The reconstruction filter is constructed from two 2-pole unity gain Sallen-Key low pass filter sections using OP27GS devices. The -3 db point is set at 2 kHz. The frequency setting capacitors use the larger 1206 form factor to provide for a wider selection of capacitor values in future revisions of the circuit.

### **Output Isolation**

The AD210SN Isolation Amplifier provides total galvanic isolation between the input and output sections, including the power supplies. It is configured for an overall gain of 1. The AD210SN has an internal 20 kHz low pass filter in its output section. See the data sheet for additional specifications on this device. The AD210SN also provides isolated +15vdc @ 5 ma to power additional output conditioning circuitry as needed. This power is available from a 2-pin header located near the associated channel's BNC connector at the front of the board.

## Digital Line

The SAMPLE\_CLK\_IO and DGND lines are routed to the board for future expansion. This line can be configures as an external clock or as a general purpose IO line. Since it is routed to each of the cards, signals on this line will be common to all cards.

## Local Voltage Regulators

The LM340 and LM7915 devices provide up to 1A of +15v and -15v, respectively from the backplane +/- 18 VDC supplies. The LM340 provides 70 db of ripple rejection with a nominal 90 uV of output noise voltage. Similarly, the LM7915 provides 70 db of ripple rejection with a nominal 375 uV of output noise voltage.

## Grounds

All of the circuits, except for the isolated input section, use power GND as their reference. The AGND from the DSP DAC module is tied to GND at one point on the card with a single trace.

#### **Test Points**

Test points are provided at the input, after each circuit section, and the output to allow for complete analysis of the channel. The test points around the filter and input are ground referenced. The final output test point is differential.

## Circuit Description

A component level description of each circuit area is presented to provide insight into the design decisions and concepts used during the development of the Output Filter Board to add in future analysis.

The board contains four identical signal channels configured for unity gain and minimal DC offset. Channel 1 (CH1) will be used as the reference design for all further discussions.

#### Buffer

The single ended output from the DSP DAC is buffered by an OP27GS device (U3) with an optional input load resistor R1 for the DAC. C5 and C6 provide power supply decoupling.

## Four Pole Butterworth Reconstruction Filter

The reconstruction filter is constructed from two 2-pole unity gain Sallen-Key low pass filters with their parameters adjusted for a cascaded operation to achieve a frequency ( $f_c$ ) response of 2 kHz. The general formulas are

$$R_{1,2} = \frac{a_i C_1 \mp \sqrt{a_i^2 C_2^2 - 4b_i C_1 C_2}}{4\pi f_c C_1 C_2}$$

(1)

$$C_2 \ge C_1 \frac{4b_i}{a_i^2} \tag{2}$$

and use the coefficients for a Butterworth filter (n=4) from Table 1.

| section | ai     | bi     | Q    |

|---------|--------|--------|------|

| 1       | 1.8478 | 1.0000 | 0.54 |

| 2       | 0.7654 | 1.0000 | 1.31 |

#### **Table 2 Low Pass Butterworth Filter Coefficients**

The Butterworth filter style was selected to provide maximum flat in-band response.

The frequency setting capacitors C7, C8, C11, and C12 use the 1206 surface mount package to provide value selections up to 4700 pf for COG high stability capacitors.

Power supply decoupling is provided through C9, C10, C13 and C14 that are placed close to their respective device power pins.

The OP27 devices are used due to their low noise characteristics. The AD27GS is the only one of the family available in a surface mount package (SO-8). The AD27EP or AD27EZ (DIP-8) should be considered in future designs due to its improved specifications.

#### **Output Isolation**

The AD210SN device (U6) decouples the system from the output transducer to reduce ground referencing problems. It provides total isolation between input, output, and power supply sections.

The gain of U3 is set to unity.

There is an integrated 20 kHz -3 db three pole low pass filter in the output section.

U6 provides an isolated power supply output of +15vdc @ 5ma maximum to power external signal conditioning components. The device does not provide short circuit protection on this output, so care should be taken when using it.

#### **Digital Line**

The SAMPLE\_CLK\_IO and DGND lines are available on the board for future use. A typical use might be to deliver an over current detection signal, derived from added circuitry, back to the DSP controller. This line would then be wire-or'd between all of the other boards.

#### Local Voltage Regulators

The LM340 (U1) and LM7915 (U2) devices provide on board voltage regulation of up to 1A of +15v and -15v respectively. They exhibit the best overall power supply noise of three terminal devices. They are mounted vertically to allow heat sinks to be attached if needed at a later date.

They each have the recommended decoupling capacitors of 0.22uF (input) and 0.1uF (output) per the manufacture's data sheets.

## Grounds

All of the circuits, except for the isolated output section, use power GND as a reference. The AGND from the DSP A/D module is tied to power supply GND at one point on the card near the P1 connector with a single 20mil trace.

## **Test Points**

Test point TP1 provided a way to monitor the output from the DSP DAC to the board and is referenced to GND. Test points TP2 (input), TP3 (midsection), and TP4 (output) are used to characterise the low pass filter and are referenced to GND. The isolated outputs of U6 are tied to TP5, which is not referenced to GND.

### Physical

The Output Filter Board conforms to IEC 297-3 for 3U EURO cards with a DIN 41612 Type C 96 pin IEC 60603-2 style connector.

The board measures 6.299 mil x 3.937 mil and is a 62 mil two layer board. The majority of the solder side is composed of a ground plane.

## **Filter Backplane**

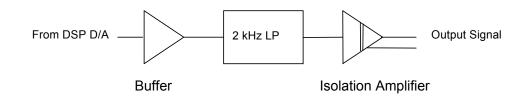

The Filter Backplane fits into a 3U Euro 19" rack and supports up to four input and four output signal conditioning cards used with the SI\_C33DSP/MOD\_6800 data acquisition and processing PC/PCI board controlled through National Instruments' LabView software.

## Overview

The backplane supports four input channel cards with each card having 4 differential channel outputs. It also supports four output cards with each card having 4 single ended inputs. The backplane supplies system level +18vdc and -18vdc that will be further regulated on each of the cards.

Since each input and output card uses the same set of interface connection, the backplane routes the individual connectors to separated banks of channel connections on the 100 pin DSP interface connector as shown in Figure 1.

Figure 3 Backplane Block Diagram

#### Layout

The card positions are spaced at 8 hp (8 x 5.08mm) and placed to meet IEC 297-3 specifications. The card connectors are female DIN 41612 (IEC 60603-2) 96 pin 3 row type C.

The 100 pin fine pitch connector (J9) and the 4 pin power connector are mounted on the solder side of the board and the 96 pin DIN connectors are all mounted on the component side.

### **Digital Line**

The SAMPLE\_CLK\_IO and DGND lines are routed to the same point on each card.

## Grounds

Signal AGND is kept separate from power GND on the backplane. They are tied together on the signal card with a single trace.

## Physical

The Filter Backplane conforms to IEC 297-3 for 19" rack 3U EURO cards with a DIN 41612 Type C 96 pin IEC 60603-2 style connector. The board measures 16.800 mil x 5.070 mil and is a 62 mil two layer board.